XC7K420T-2FFG901I - Интеграль схемалар, урнаштырылган, кыр программалаштырылган капка массивлары

Продукт сыйфатлары

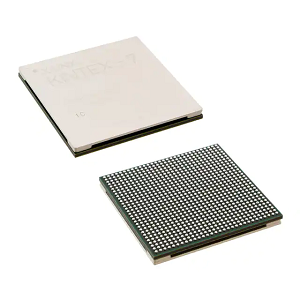

| ТYР | ИЛЛУСТРАТ |

| категориясе | Интеграль схемалар (IC)Урнаштырылган Кыр программалаштырыла торган капка массивлары (FPGAs) |

| җитештерүче | AMD |

| сериясе | Kintex®-7 |

| төрү | поднос |

| Продукция статусы | Актив |

| DigiKey программалаштырылган | Тикшерелмәгән |

| LAB / CLB номеры | 32575 |

| Логик элементлар / берәмлекләр саны | 416960 |

| RAM битләренең гомуми саны | 30781440 |

| I / Os саны | 380 |

| Вольт - электр белән тәэмин итү | 0.97В ~ 1.03В |

| Урнаштыру төре | Faceир өсте ябыштыргыч төре |

| Эш температурасы | -40 ° C ~ 100 ° C (TJ) |

| Пакет / Торак | 900-BBGA 、 FCBGA |

| Сатучы компоненты анкапсуляциясе | 901-FCBGA (31х31) |

| Продукциянең мастер номеры | XC7K420 |

| ТYР | ИЛЛУСТРАТ |

| категориясе | Интеграль схемалар (IC)Урнаштырылган |

| җитештерүче | AMD |

| сериясе | Kintex®-7 |

| төрү | поднос |

| Продукция статусы | Актив |

| DigiKey программалаштырылган | Тикшерелмәгән |

| LAB / CLB номеры | 32575 |

| Логик элементлар / берәмлекләр саны | 416960 |

| RAM битләренең гомуми саны | 30781440 |

| I / Os саны | 380 |

| Вольт - электр белән тәэмин итү | 0.97В ~ 1.03В |

| Урнаштыру төре | Faceир өсте ябыштыргыч төре |

| Эш температурасы | -40 ° C ~ 100 ° C (TJ) |

| Пакет / Торак | 900-BBGA 、 FCBGA |

| Сатучы компоненты анкапсуляциясе | 901-FCBGA (31х31) |

| Продукциянең мастер номеры | XC7K420 |

FPGAs

Уңай яклары

FPGAларның өстенлекләре түбәндәгечә:

(1) FPGAлар логик күзәнәкләр, RAM, мультипликаторлар һ.б. кебек җиһаз ресурсларыннан тора, бу җиһаз ресурсларын рациональ рәвештә оештырып, мультипликаторлар, реестрлар, адрес генераторлары һ.б.

(2) FPGAлар блок схемалары яки Verilog HDL ярдәмендә эшләнергә мөмкин, гади капка схемаларыннан FIR яки FFT схемаларына кадәр.

.

. арттырылырга тиеш, ләкин хәзерге IC процесслары һәм башка факторлар белән идарә ителә).

Кимчелекләр

FPGAларның кимчелекләре түбәндәгечә:

(1) FPGAлар барлык функцияләр өчен аппаратны тормышка ашыруга таяналар һәм шартлы сикерүләр кебек операцияләрне тормышка ашыра алмыйлар.

(2) FPGAлар бары тик төп нокталы операцияләрне генә башкара ала.

Йомгаклау: FPGAлар барлык функцияләрне тормышка ашыру өчен җиһазларга таяналар һәм тизлек ягыннан махсус чиплар белән чагыштырып була, ләкин гомуми максат процессорлары белән чагыштырганда дизайн сыгылмасында зур аерма бар.

Дизайн телләр һәм платформалар

Программалаштырыла торган логик җайланмалар - EDA технологиясе ярдәмендә электрон кушымталарның билгеләнгән функцияләрен һәм техник спецификацияләрен конкретлаштыручы аппарат йөртүчеләр.FPGAs, бу юлны тормышка ашыручы төп җайланмаларның берсе буларак, турыдан-туры кулланучыларга юнәлтелгән, бик сыгылучан һәм күпкырлы, куллану җиңел, һәм аппаратта тиз сынап карау.

Hardwareиһазлау тасвирлау теле (HDL) - санлы логика системаларын проектлау һәм санлы схемаларны сурәтләү өчен кулланыла торган тел, еш кулланыла торган төп VHDL, Verilog HDL, Verilog системасы һәм С системасы.

Hardwareәрбер катлаулы аппарат тасвирлау теле буларак, бик югары тизлектәге интеграль схема җиһазларын тасвирлау теле (VHDL) махсус аппарат челтәреннән бәйсез һәм дизайн платформасыннан бәйсез, киң диапазон тасвирлау мөмкинлеге өстенлекләренә ия. конкрет җайланмаларга бәйле, һәм катлаулы контроль логиканың дизайнын каты һәм кыска кодта сурәтләү сәләте һ.б. Бу күп EDA компанияләре тарафыннан хуплана һәм электрон дизайн өлкәсендә киң кулланыла.киң кулланыла.

VHDL - схема дизайны өчен югары дәрәҗәдәге тел, һәм башка аппарат тасвирлау телләре белән чагыштырганда, ул гади тел, сыгылучылык һәм җайланма дизайныннан бәйсезлек характеристикасына ия, аны EDA технологиясе өчен уртак аппарат тасвирлау теле итә һәм EDA технологиясен күбрәк итә. дизайнерлар өчен мөмкин.

Verilog HDL - киң кулланылган җиһаз тасвирлау теле, ул модельләштерү, синтез һәм симуляцияне кертеп, җиһаз проектлау процессының берничә этапында кулланыла ала.

Verilog HDL өстенлекләре: Ска охшаган, өйрәнү җиңел һәм сыгылмалы.Регистрны исәпләп.Стимул язуда һәм модельләштерүдә өстенлекләр.Кимчелекләр: күп хаталарны компиляция вакытында табып булмый.

VHDL уңай яклары: каты синтаксис, ачык иерархия.Кимчелекләр: озак танышу вакыты, җитәрлек сыгылмас.

Quartus_II программа тәэминаты - Altera тарафыннан эшләнгән тулы күп платформа дизайн мохите, ул төрле FPGA һәм CPLDларның дизайн ихтыяҗларын канәгатьләндерә ала, һәм чипта программалаштырыла торган система дизайны өчен комплекслы мохит.

Vivado Design Suite, FPGA сатучысы Xilinx тарафыннан 2012-нче елда чыгарылган интеграль дизайн мохиты. Бу югары интеграль дизайн мохитен һәм системадан IC дәрәҗәсенә кадәр яңа буын коралларын үз эченә ала, барысы да уртак масштаблы мәгълүмат моделе һәм уртак көйләү мохите нигезендә төзелгән.Xilinx Vivado Design Suite дизайнга җиңел кулланыла ала торган FIFO IP үзәкләрен тәкъдим итә.